Arquitetura e Verificação de um Sistema Digital Baseado na Criptografia AES 128 Bits

Palabras clave:

AES, Criptografia, HDL, Segurança de Hardware, Verificação Funcional, VerilogResumen

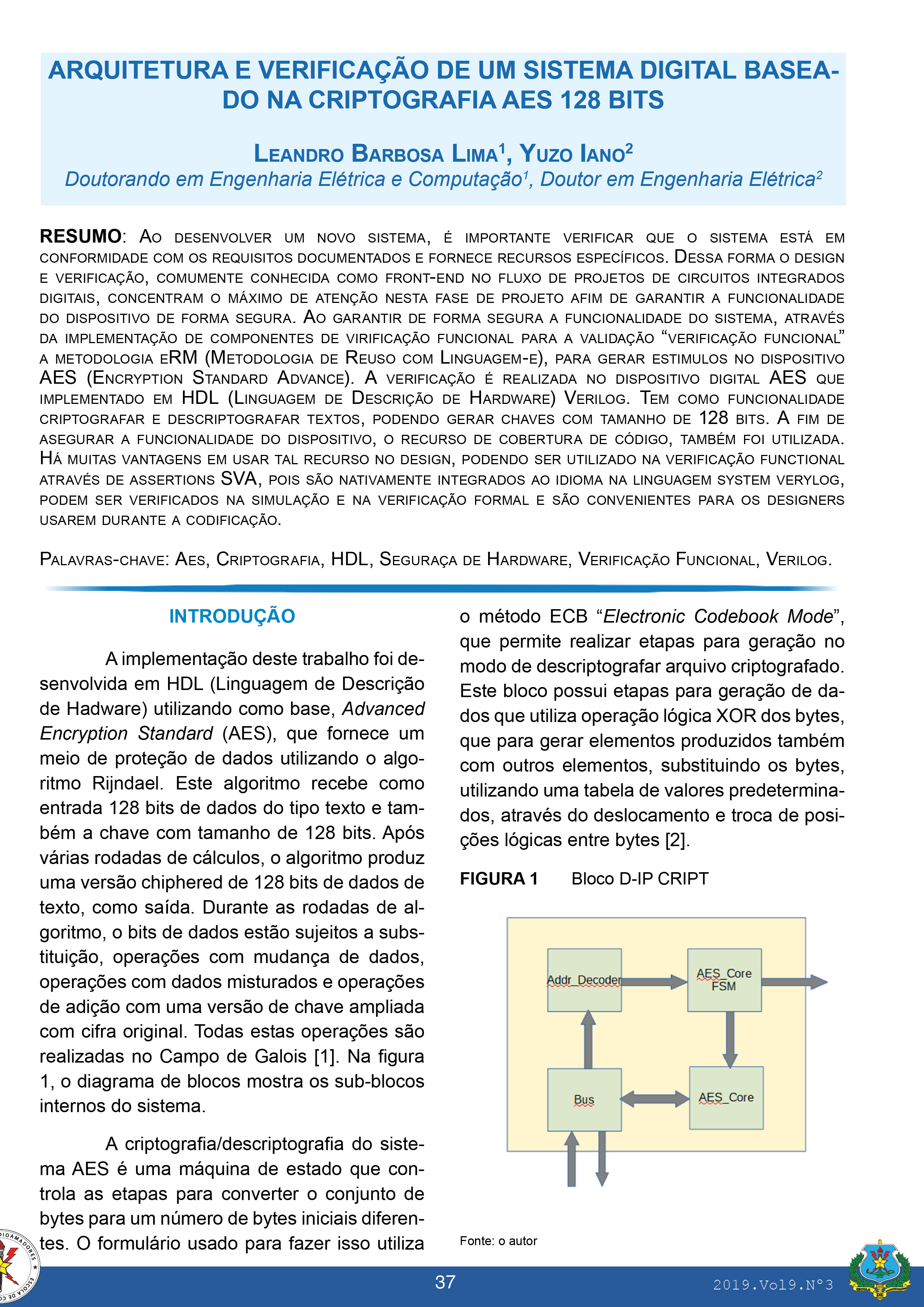

Ao desenvolver um novo sistema, é importante verificar que o sistema está em conformidade com os requisitos documentados e fornece recursos específicos. Dessa forma o design e verificação, comumente conhecida como front-end no fluxo de projetos de circuitos integrados digitais, concentram o máximo de atenção nesta fase de projeto afim de garantir a funcionalidade do dispositivo de forma segura. Ao garantir de forma segura a funcionalidade do sistema, através da implementação de componentes de virificação funcional para a validação “verificação funcional” a metodologia eRM (Metodologia de Reuso com Linguagem-e), para gerar estimulos no dispositivo AES (Encryption Standard Advance). A verificação é realizada no dispositivo digital AES que implementado em HDL (Linguagem de Descrição de Hardware) Verilog. Tem como funcionalidade criptografar e decriptografar textos, podendo gerar chaves com tamanho de 128 bits. A fim de assegurar a funcionalidade do dispositivo, o recurso de cobertura de código, também foi utilizada. Há muitas vantagens em usar tal recurso no design, podendo ser utilizado na verificação funcional através de assertions SVA, pois são nativamente integrados ao idioma na linguagem System Verylog, podem ser verificados na simulação e na verificação formal e são convenientes para os designers usarem durante a codificação.

Descargas